AMD's Venice: Zen 6 EPYC CPU Die Unveiled – A Glimpse into the Future of Server Processing

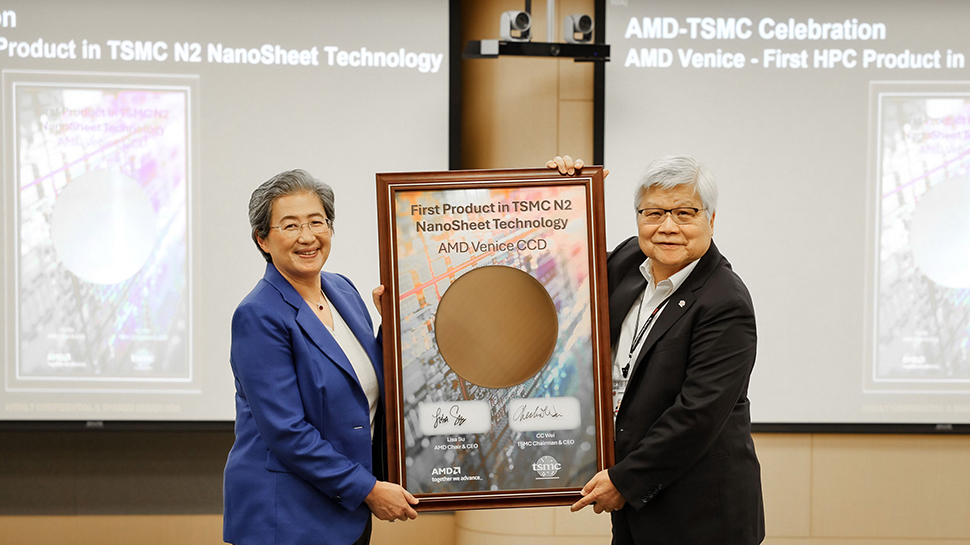

AMD has officially unveiled the die of its next-generation server processor, codenamed "Venice," based on the highly anticipated Zen 6 architecture. This unveiling offers a first look at the intricate silicon powering the upcoming EPYC processors, hinting at significant performance improvements and enhanced capabilities for data centers worldwide. While specific details remain scarce, the image released provides intriguing insights into the chip's density and complexity.

What We Know (and Don't Know) About Venice:

The image of the Venice die showcases a densely packed chip, reflecting the advanced manufacturing process likely employed by AMD. This density suggests a significant increase in core count and potentially improved performance per watt compared to its predecessors. However, AMD has remained tight-lipped about the precise specifications, including:

- Core Count: While speculation abounds, the exact number of cores in the Venice-based EPYC processors remains unconfirmed. Industry analysts predict a substantial increase compared to the current Zen 4 generation.

- Clock Speeds: Similarly, the clock speeds for these processors are yet to be disclosed. Higher clock speeds are anticipated, leading to faster processing speeds and improved overall performance.

- Cache Size: Increased cache size is expected to improve performance and reduce latency, critical factors for demanding server workloads.

- Manufacturing Process: Although not explicitly stated, the die's density strongly suggests a move to a more advanced node, possibly 3nm or an enhanced version of the existing 5nm process.

The Significance of Zen 6 and the Venice Die:

The unveiling of the Venice die represents a crucial milestone in AMD's ongoing competition with Intel in the server processor market. Zen 6 promises significant architectural improvements, potentially surpassing the performance gains seen with previous generations. This translates to:

- Improved Performance: Faster processing speeds and increased core counts will lead to faster completion times for demanding tasks like virtualization, database management, and high-performance computing (HPC).

- Enhanced Efficiency: Improvements in power efficiency are crucial for data centers, reducing operating costs and minimizing environmental impact.

- Advanced Features: We can expect new and improved features to support emerging technologies like AI and machine learning, further solidifying AMD's position in the server market.

Implications for the Data Center Industry:

The Venice-based EPYC processors are expected to have a significant impact on the data center landscape. Their improved performance and efficiency can lead to:

- Increased Scalability: Data centers can handle larger workloads with fewer servers, leading to reduced infrastructure costs.

- Reduced Energy Consumption: Enhanced power efficiency directly translates into lower energy bills and a smaller carbon footprint.

- Faster Application Deployment: Improved processing power allows for faster deployment and execution of applications, leading to improved business agility.

Looking Ahead:

While official launch dates and pricing remain undisclosed, the unveiling of the Venice die generates considerable excitement within the industry. AMD's continued innovation in the server processor market promises a future of increasingly powerful and efficient data center solutions. We eagerly await further details and the official launch of these next-generation EPYC processors. Stay tuned for updates as more information becomes available.

Keywords: AMD, EPYC, Zen 6, Venice, Server Processor, CPU, Die, Data Center, HPC, AI, Machine Learning, Intel, Performance, Efficiency, Manufacturing Process, 3nm, 5nm, Core Count, Clock Speed, Cache Size.